Two Decades of Experience in High-Performance Backplane Design and Simulation

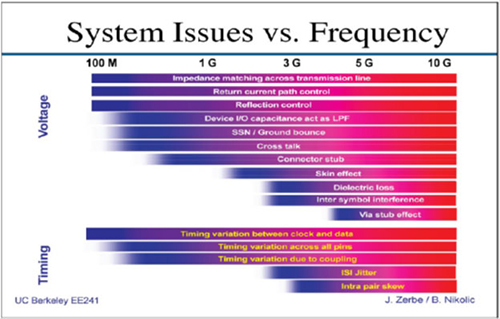

An important characteristic of an electronic control system that must be given careful attention is signal integrity. The signal becomes more susceptible to attenuation due to ringing, crosstalk, ground bounce, distortion, signal loss, and power supply noise as the bit rates become more extreme. It is important to mitigate these effects on all levels of electronic design including electronic packaging, internal connections of integrated circuitry, through the chassis design, the Printed Circuit Boards (PCB), the backplane, and connections between different sub-systems. Curtiss-Wright has over two decades of experience in high-performance backplane design and simulation; having performed Signal Integrity analysis and design for numerous application-specific switch fabric backplane designs. Our personnel has experience in performing full 3D modeling and simulation of interconnects at frequencies up to 20 GHz.

High Speed Signal Integrity Capabilities

Curtiss-Wright Defense Solutions is a leader in the implementation of high-speed serial fabric signaling on VPX/OpenVPX™ platforms. We have been there every step of the journey:

- From the introduction of VPX with Gen 1 protocols (e.g. Serial Rapid IO @ 2.5-3.125 Gbaud, PCI Express™ Gen 1 @ 2.5 Gbaud)

- To Gen 2 (e.g. Serial Rapid IO @ 5-6.25 Gbaud, PCI Express Gen 2 @ 5.0 Gbaud)

- Through Gen 3 (40G Ethernet @ 10.3125 Gbaud, Infiniband QDR @ 10.0 Gbaud, PCI Express Gen 3 @ 8 Gbaud)

Developing, introducing and deploying world-leading products at each stage. Work on Gen 4(PCI Express @ 16 Gbaud) has been ongoing for more than a year, and product timing will be coordinated with silicon availability, among other factors.

Design Considerations

Curtiss-Wright has developed an advanced signal integrity analysis methodology and post-processing to ensure quality design of our electronic systems, able to support Gen3 data rates. Much of our analysis is based on the IEEE 802.3-2008 including:

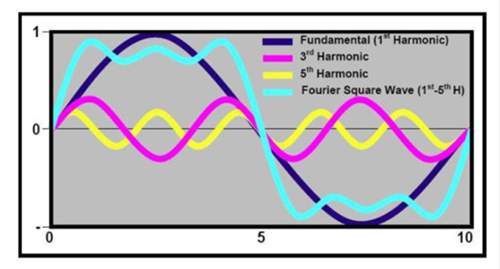

- Frequency domain analysis

- Post-processing

- Time analysis (Eye Diagrams)

- BER analysis

Along with other design considerations such as:

- Insertion Loss

- Fitted Attenuation

- VPX return loss

- Insertion Crosstalk Ratio

These types of design considerations extensive studies have been performed on Gen3 signaling on VPX backplanes. In addition, VITA 68 VPX Compliance Channel draft is consistent with our analysis methodology; which is applied to define channel characteristics for multiple fabric types. As we continue to optimize our control system design to be consistent with Gen3 requirements, significant investment has been made by Curtiss-Wright in the analysis and testing to ensure Gen3 performance.

Design Tools

We have the industry's leading signal integrity analysis tools:

- HFSS 3D field solver

- ADS frequency domain and statistical analysis

- Curtiss-Wright post processing algorithms

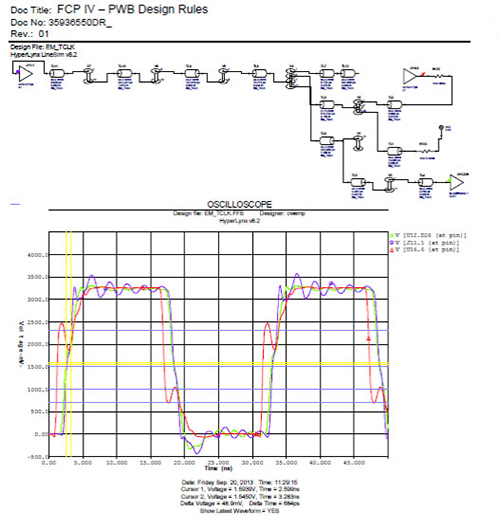

- HyperLynx Virtual Simulation Software

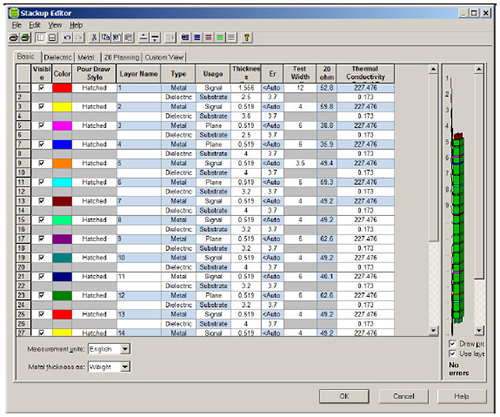

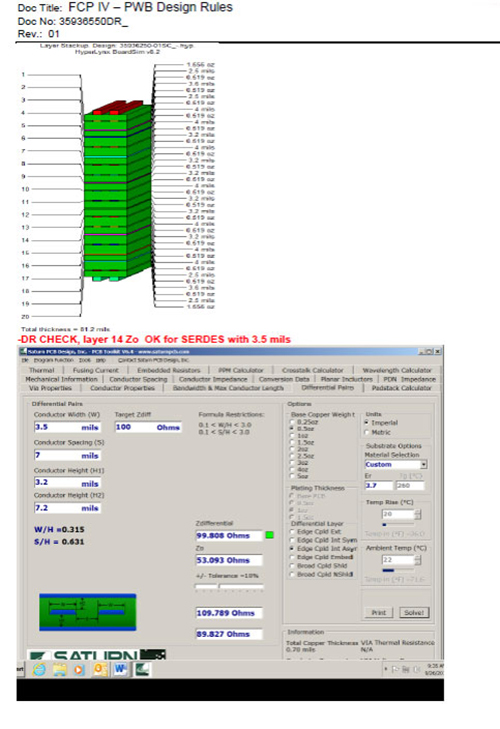

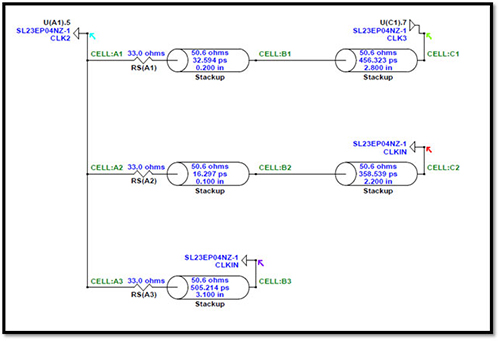

| Post Routing Signal Integrity Verification - HyperLynx | Design Stack up Impedance Verification – HyperLynx |

|

|

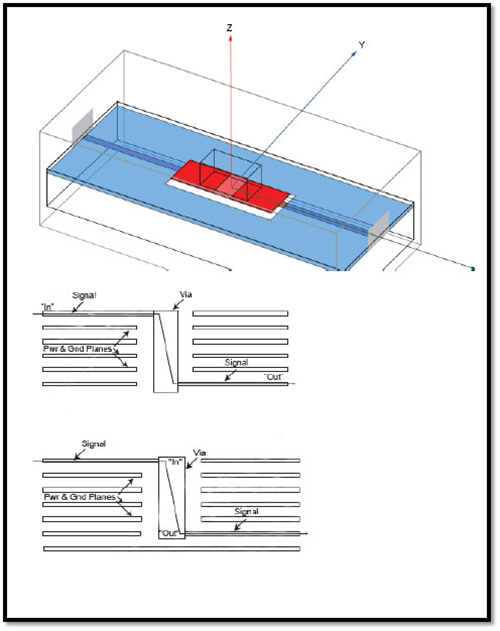

| Design Rules Stack-up Verification Check – HyperLynx | 2D Simulation using Frequency Domain Analysis – HyperLynx |

|

|

A few important characteristics to look at during the design phase are:

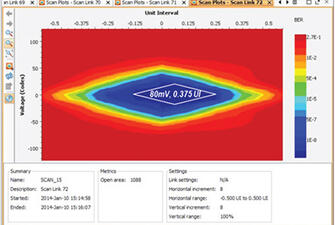

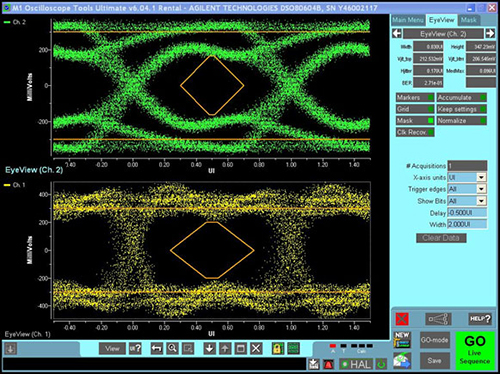

- Simulated Eye Diagrams allow evaluation of the channel's net ability to transmit data

- Simulated TDR and TDT are also available for investigating discontinuities in the signal path

- Frequency domain analysis including calculated parameters for 1000BASE-KX, 10GBASE-KX4, 10GBASE-KR, 40GBASE-KR4 and VITA 68 compliance

- Statistical Eye Diagrams

- Statistical analysis including bathtub curves for BER

| Pre Route Signal Integrity Simulation – HyperLynx | Rise Time and Bandwidth Graph |

|

|

| Design Considerations at High Frequencies | Functional Test on Eye Diagram, Leads to Higher Reliability |

|

|

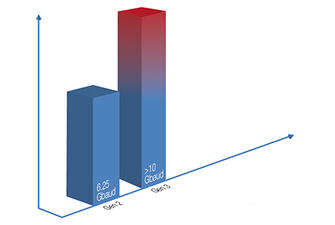

Key Design Milestones

Through internal testing and modeling research, Curtiss-Wright has been able to achieve robust solutions in Gen3 signaling in Open VPX systems greater then 10GBaud. Our partner's Fabric40 backplanes incorporate patent-pending optimizations to deliver the very best performance, and these design optimizations are being migrated to our wide range of Fabric 40 payload modules, including SBCs, DSPs, FPGAs, and switches. It really comes down to a commitment to high level signal integrity engineering. Curtiss-Wright has the capability to meet and exceed the requirements of Gen3 signaling due to our comprehensive analysis and experience.

Gen3 OpenVPX Backplanes Supporting 10.3 Gbaud Signaling in OpenVPX Systems

Curtiss-Wright Defense Solutions has done extensive research to develop highly optimized 10G compliant design techniques for attaining reliable and robust signal integrity performance with Gen3 OpenVPX systems. We continue to work on maximizing signal integrity performance for next gen standards. Our Fabric40 family of products addresses the current generation design challenges.

Applications

Modern day high performance systems require world class signal integrity capabilities. Many of today’s standard switched fabrics are operating at 5 Gbaud to 6.25 Gbaud, with leading edge products such as Curtiss-Wright’s Fabric40 products operating at >10 Gbaud. Examples of these higher speeds are: Gen3 PCIe at 8 Gbaud, InfiniBand QDR at 10 Gbaud, and Ethernet 40GBase-KR4 at 10.3 Gbaud. We have performed signal integrity simulation studies for standard groups in developing several standard backplanes. In applications ranging from PICMG 2.16 to VXS, VPX, or custom backplanes, Curtiss-Wright is the vendor of choice for high-speed backplane signaling.