Synthetic Aperture Radar (SAR) and Electronic Warfare (EW) systems process complex waveforms and require real-time performance to keep up with the incoming data. At 3 GHz, a Central Processing Unit (CPU) core can execute about 3 Giga-Ops per second, and a quadcore CPU can execute about 12 Giga-Ops per second. Meanwhile, Field Programmable Gate Arrays (FPGA) contain thousands of hardened Digital Signal Processing (DSP) cores that can operate at 100s of MHz, can process Tera-Ops per second. When the front-end of the latest signal processing systems have to process multiple data streams at multi-gigabit rates, designers turn to FPGA to meet their demanding processing needs.

FPGA-based commercial off-the-shelf (COTS) modules are now essential components for radar and EW systems, delivering tremendous levels of DSP performance with thousands of cores per FPGA. Unfortunately, FPGA design cost is much higher than software design, typically requiring six to twelve months of development after the software algorithms have been frozen. According to Moore's Law, FPGA capacity doubles every 18 months, and design teams quickly lose the ability to keep up.

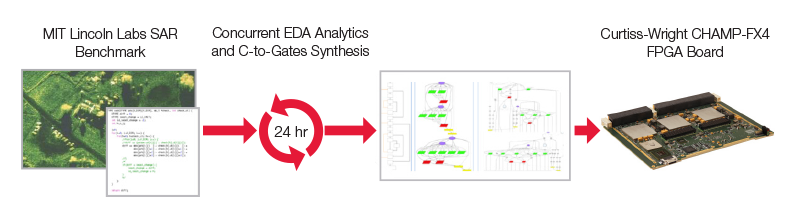

This paper examines the benefits of combining multiple FPGAs with the use of a C-to-Gates design flow to help reduce the heavy investment of a long design process. The DARPA HPCS SAR Benchmark is an example of a complex algorithm that needs to be implemented in an FPGA. We explore how three FPGAs on one board can provide unprecedented computational power and communication bandwidth. We will also explore how adding C-to-Gates tools can help rapidly convert software algorithms to maximize performance while reducing engineering costs.

Download the white paper to learn more.