Defense platforms and their associated physically constrained payloads have long been the limiting factor in terms of mission capability. In other words, there is a set power budget available, maximum weight and volume limits, and a fixed ceiling of heat that can be removed depending on the particular platform-based payload. Whatever processing can be performed in this fixed size, weight, and power (SWaP) envelope dictates and limits mission capability associated with the particular function of the payload.

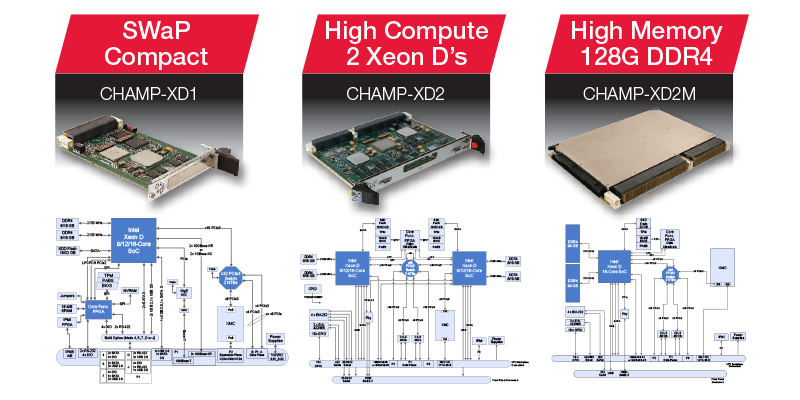

Given the mandate to maximize performance for a given enclosure, the defense industry has largely gravitated towards using a mixture of heterogeneous processing elements with the idea being that developers play to the strengths of these individual elements, applying them to the most appropriate sensor processing stage. Three of the biggest contenders have been FPGAs, GPPs, and GPGPUs. FPGAs and GPGPUs have experienced tremendous strides in terms of processing densities. However, General Purpose Processors (GPPs) have not been experiencing this same rapid gain in functionality, for instance being limited to four cores as with the case of the Intel® Core™ i7 family. That is until now, where the GPP has been propelled forward, with the advent of a new multi-core Intel architecture family, the Xeon® D. This white paper will explore the technology behind the Xeon D’s flexibility and how it can solve a diverse range of military and aerospace challenges.

Download the white paper to learn more.

- Intel Xeon D

- Using a common technology for multiple applications

- Maximizing compute power

- Overcoming sensor fusion challenges

- Tackling the mobile server