In the past, CameraLink has relied upon ChannelLink buffer chip sets to implement parallel to serial conversion using word sizes and data rates. ChannelLink is the interface that CameraLink is built on. For years, bespoke IO cards have been required with interfaces that were ChannelLink/CameraLink only. Today’s parallel interfaces are now fast enough to drive these IO channels directly using “generic” FPGA products. This works well for flexibility and provides an easier migration path for legacy CameraLink IO. Care should be taken as buffer devices also provide protection to the host FPGA. FPGA IP can mimic the internal parallel to serial conversion for ChannelLink along with the higher-level CameraLink layers.

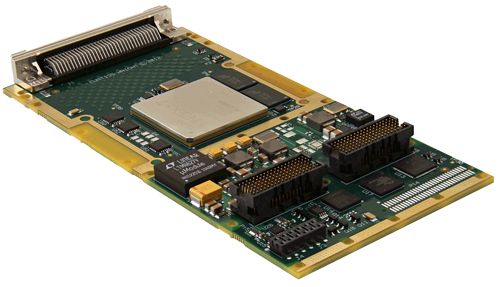

Custom requirements can provide a conduction-cooled solution. Curtiss-Wright’s XF07-523 FPGA Digital IO XMC card offers greater flexibility without the need of developing hardware specifically designed for CameraLink.

XF07-523 FPGA Digital IO XMC

The XF07-523 Solution.

The XF07-523 is a Kintex-7 based XMC. Available in the conduction-cooled format it includes:

- Front panel (air cooled only), a PMC P14/XMC P16 digital IO

- Xilinx Kintex-7 FPGA K325T, speed grade 2 FPGA

- Sufficient IO for multiple CameraLink channels of different types and

- FusionXF for VxWorks or Linux software for embedding an application within the FPGA option

The XF07-523 offers the flexibility of using newer generation FPGAs to drive several CameraLink IO ports in different modes. The result is a conduction-cooled configuration without the added cost of new hardware development making the XF07-523 ideal for demanding applications.

Find out more about CameraLink by reading the Case Study: Rugged CameraLink using Xilinx Kintex-7 FPGA