The many sensors on today’s defense and commercial platforms produce tons of data requiring a massive amount of quick and efficient processing to achieve mission success. System integrators must apply substantial resources to achieve performance and functional compliance, slowing development, system integration and delaying time to market.

However, new and existing standards are making it easier to leverage innovative, multi-vendor, open-architecture building blocks for rugged embedded solutions. With standards-based, pre-integrated, and pre-validated Commercial-Off-The-Shelf (COTS) building blocks, system integrators are able to reduce program risk, accelerate development-to-deployment, and build quality, cost-efficient High-Performance Embedded Computing (HPEC) systems that deliver Size, Weight, Power, and Cost (SWaP-C) for defense applications.

System integrators can meet Quick Reaction Capability objectives by leveraging existing ecosystems of pre-integrated, pre-validated COTS building blocks.

Sensor development is expected to follow an open architecture model in the coming years as Sensor Open System Architecture (SOSA) standards reach maturity and as defense and aerospace customers define requirements that use open standards for programs.

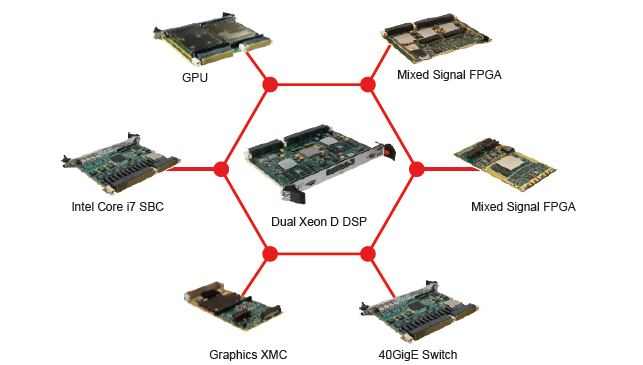

Figure 1: Open Standard, Open Architecture HPEC System

The Wright Choice

Anticipating the future, Curtiss-Wright is providing its customers the building blocks to stay ahead of the development curve. The strategic alliance between Curtiss-Wright, WOLF Advanced Technology, and Dolphin Interconnect Solutions help ease development and integration efforts by optimizing the performance of Curtiss-Wright’s GPGPU COTS-based modules. These optimized, pre-validated, pre-integrated COTS building blocks reduce subsystem development costs, time to market, and overall program schedule risk, while improving quality.

Scalability can be achieved from a range of available CHAMP-XD1, CHAMP-XD2, and CHAMP-XDM Xeon D processors.

Key Features delivering scalability:

- 25W XMC slot

- up to 32 lanes of PCIe Gen 3 for WOLF’s OpenVPX 3U and WOLF’s OpenVPX 6U GPU module interconnect and expansion

- 16 slot 6U OpenVPX systems can be developed to provide 100+ TFLOPS of FPGA, GPP, and GPGPU accelerator peak processing capability

You can find out more about how to minimize risk with open standard, open architecture HPEC systems by reading our white paper: Simplifying Sensor Data Processing with Advanced GPGPU Technology and COTS Building Blocks