While some system developers maintain their traditional antipathy to a “Not Built Here” approach, the continued maturation of the COTS industry and the evolution of robust, well-supported open standards has in recent years annihilated the most common arguments against having hardware platform integration be handled by a trusted partner.

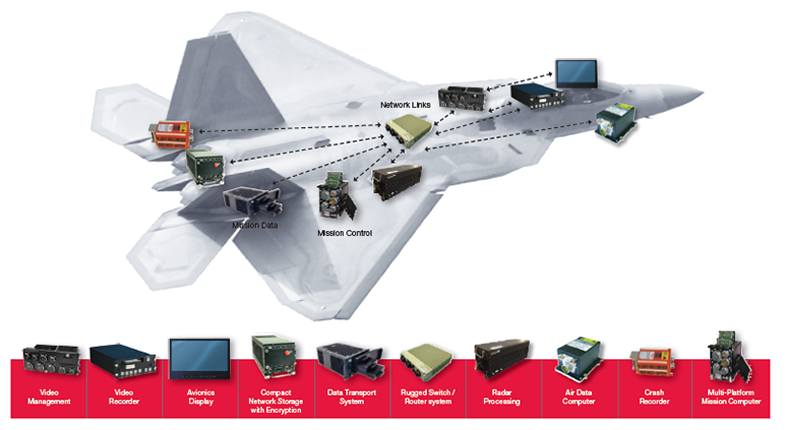

A vendor like Curtiss-Wright Defense Solutions is an expert in open system standards, COTS modules, backplanes, power architectures, and the challenges of ruggedized packaging and thermal management – all critical competencies for providing stable application-ready hardware platforms for system integrators.

The strongest rebuttal to “Not Built Here” is the simple fact that the vendor who designs and develops the COTS modules – the single board computers, DSP engines, FPGA cards, networking switches, etc. – and has led the development of the underlying open system standards is already expert at integrating these very same modules, which results in technology familiarity and learned lessons that eliminate integration risk. In other words, any potentially thorny interoperability challenges have already been identified, addressed, and resolved numerous times by work done on similar systems.

This white paper discusses ways to reduce program risks and development time by eliminating embedded systems design risks such as interoperability issues.

Download the white paper to learn more.