The Challenge of SWaP for FPGAs

With every new generation of design, we expect something better than the last. The iPhone is a perfect example: with every release, the public is keen to see what new features they can discover. When dealing with rugged, high-temperature environments, designing for a better next-generation product has a special set of its own engineering challenges.

Size, weight, and power (SWaP) are a cornerstone for many defense applications along with cost and performance. However, these parameters are not always team players, so a choice needs to be made or at the very least compromises for the best overall solution. FPGA-based designs are often seen as the most power-hungry designs, and IO devices are getting much smaller while performance is also increasing. As we pack more power into a smaller space, can it be properly cooled? Where are the problem areas? What are the trends? Where should we pay attention? Do you want to buy from a supplier who focuses only on functionality?

A prime example of this is high-speed acquisition systems using newer FPGAs: Newer FPGAs offer more resources and higher speed, but does that mean lower power too? Not always. There is often a familiar non-committal phrase: “it depends”. FPGA evolution results in lower power per gate between generations due to smaller geometries and new structures such as FinFETs. The power reduction between generations is often cited to be around 30% per gate. These figures come with conditions depending on whether this is static, dynamic, or even temperature-related. Occasionally power per gate saving is up to 50% power reduction. These power reductions are decent, but newer generation FPGA devices would typically double the gate density too, so if the addition of new algorithms with a similar overall utilization, the board level FPGA design may well end up hotter than its predecessor. In blank terms, this is a pain point.

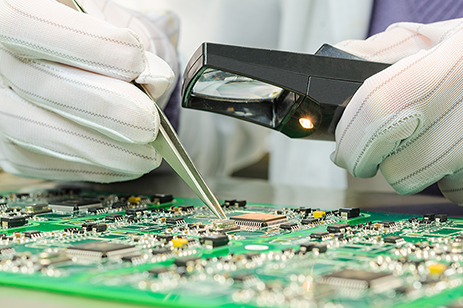

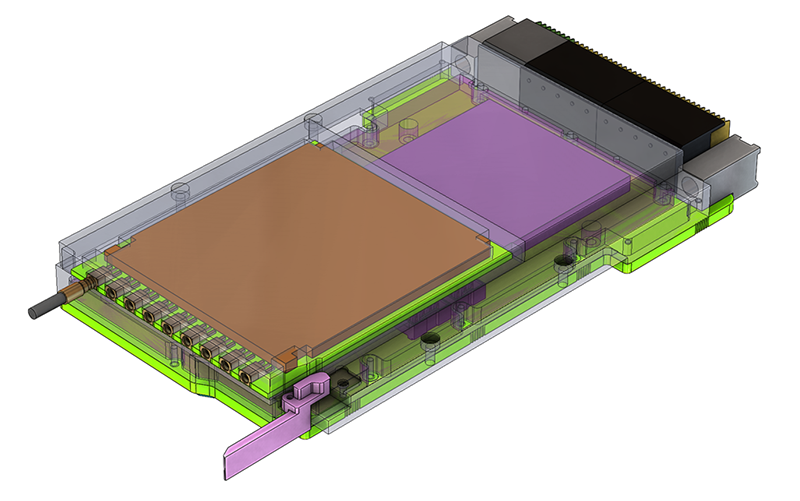

Figure 1: Functionality, higher power, and smaller spaces creates system challenges

In this white paper, we’ll explore the issue of cooling FPGAs as well as other challenges in FPGA-driven high-speed data acquisition systems.

Download the white paper to learn more.

- FPGA cooling challenges

- JESD204B

- Shrinking technology

- Heat density

- Wider temperature requirements

- Wider system demands