# Panavia and the KAD/PBM/001

TEC/NOT/009

This paper outlines the key features of the KAD/PBM/001 with respect to Panavia bus monitoring. It is recommended that *TEC/NOT/008 - Panavia*, be read first. For a list of error codes and output register definitions, refer to the *KAD/PBM/001* data sheet.

The following topics are discussed:

- "6.1 The physical layer" on page 1

- "6.2 Bit detection circuitry" on page 1

- "6.3 Word detection circuitry" on page 2

- "6.4 Error reporting, word counting and time tagging" on page 2

- "6.5 Parsing" on page 3

- "6.6 Snarfing" on page 3

- "6.7 Conclusion" on page 4

#### 6.1 The physical layer

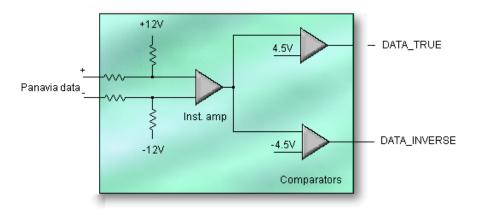

The KAD/PBM/001 monitors up to eight Panavia busses. The following figure displays the receiver circuit internal to the KAD/PBM/001.

Figure 6-1: One of eight receivers on the KAD/PBM/001 (same circuit used for clock)

The thresholds for High and Low are +4.5V and -4.5V respectively. As per the Panavia specification, the shields for each bus must be connected to the GND pin of the KAD/PBM/001.

#### 6.2 Bit detection circuitry

Each of the eight busses has a separate independent bit detection circuit.

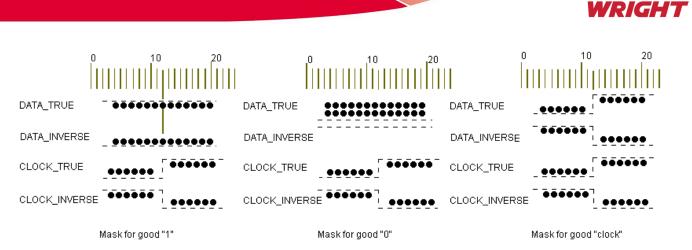

The true/complement output of the receiver is sampled at 25 times the selected bit-rate. The output of the bit detection circuitry is: 1, 0, clock or bad. The following figure displays patterns used for determining good 1, 0 or clock.

Figure 6-2: Masks for 1, 0 or clock

The gradation displayed in the previous figure represents 25 samples per bit period. The KAD/PBM/001 is tolerant of jitter because data is not checked either side of an expected transition (indicated by the absence of dots).

The bit detector outputs a bad indication if one of the three masks is not met after a 1, a 0 or a clock has been received. In other words a 1, a 0, a clock or a bad is clocked into the serial to parallel register of the word detection circuitry every bit period.

# 6.3 Word detection circuitry

Each bus has a separate word detection circuit. A word is considered found when three clock bits follow at least eight good 1s or 0s.

This circuit checks that there is precisely the correct number of good bits, the spare[3:1] bits are 0 and the parity is correct. The Tag[4:0] and control bit along with 3 bits indicating the bus are used to address a trigger list. The trigger list assigns one of 256 identifiers (IDs) to each word along with flags for invalid tag, control bit error and also returns the next expected tag for sequence checking (if enabled).

The output of the word detection circuitry consists of the following:

| Flags         | Indicating invalid tag, control bit error, parity error, not enough bits or sequence error (when the tag was not the expected tag). |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Traffic[15:0] | All the bits in the word received except the tag[4:0], control, spare[3:1] and parity.                                              |  |

| ID[7:0]       | One of 512 IDs based on bus[2:0], tag[7:0] and control bit.                                                                         |  |

| Time[47:0]    | The binary coded decimal (BCD) time, to hours of day, with ms resolution, at the midpoint of the first bit received.                |  |

| Word[15:0]    | The (valid) word counter for each bus when the word arrived.                                                                        |  |

Because the data transfer is word based (not messages or frames), there is no protocol tracking on the KAD/PBM/001. A received word either has errors or it does not.

### 6.4 Error reporting, word counting and time tagging

The errors detected by the bit detection and word detection circuitry are combined into a 4-bit code. This code can be part of the report parameter from the KAD/PBM/001, along with 3 bits indicating the bus on which the fault was recorded (see the *KAD/PBM/001* data sheet).

All errors are also reported/logged via the snarfer along with the time that it occurred and the traffic following.

When a valid word is received, a word counter is incremented for each bus. This is a 16-bit binary counter that resets at FFFF hex. This parameter can be read for each of the eight busses from the KAD/PBM/001.

The following three binary coded decimal (BCD) time words are associated with time tagging:

| High time  | 00:00 | →23:59 Hrs:Mins |

|------------|-------|-----------------|

| Low time   | 00.00 | →59.99 seconds  |

| Micro time | 0000  | →9999 *s        |

# 6.5 Parsing

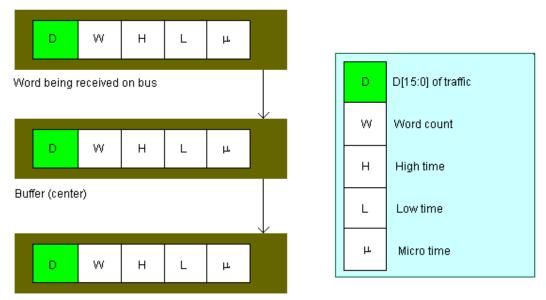

In the KAD/PBM/001 parser, triple buffering of words and tags is used for each bus as shown in the following figure.

Word being read on KAM-500 backplane

Time tags and a word count are added to each word received, and stored in separate buffers for each of the eight busses. As soon as a word is received with no errors, the complete buffer is transferred to the center buffer. If the data in the center buffer has not been transferred to a read buffer, a skipped bit is set.

As soon as the last parameter of interest has been read from the buffer being read by the backplane, the contents of the center buffer (if new) are transferred to the read buffer. If no new word has been received, the stale flag is set. A center and read buffer exist for every ID (1024).

# 6.6 Snarfing

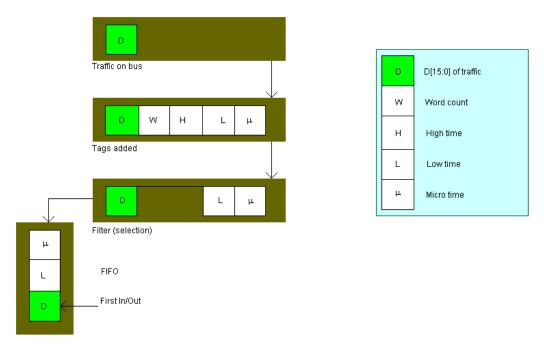

One disadvantage of parsing is that data can be lost (skipped). One solution is to store all traffic (or selected traffic) and tags in a FIFO as shown in the following figure.

In the snarfer, all traffic (words) are first tagged with High, Low and Micro time and the word count, for that bus, when the word arrived.

Traffic and tags are then filtered (removed) according to user-defined filters depending on the word ID and how full the FIFO is (empty to 1/4, 1/4 to 1/2, 1/2 to 3/4, or 3/4 to full). Only the traffic words and Low time tag are allowed through (see the following figure).

If an error occurs, an error code, all traffic, the word count and the three time tags of each command word are sent to the FIFO.

A single FIFO (16K deep) is shared between all eight busses. A content identifier is added to each traffic or tag word, identifying the type of parameter (data Hi/Lo, Time Hi/Lo/ $\mu$ , word count, error or FIFO full/empty) and the bus the traffic was received on.

### 6.7 Conclusion

Key features of the KAD/PBM/001 include:

- · Eight valid word counters, one for each bus.

- A 48-bit binary coded decimal (BCD) timer that counts to hours of the day with 1 μs resolution. The timer is used to tag data to 1 μs resolution and is typically seeded from an IRIG-B module (KAM/TCG/001) in the same chassis.

- Valid words defined and identifiers are assigned (one of 256 IDs) using all the bits of the tag and bus number. Multiple words can be mapped to any ID.

- Parsing of traffic from up to 256 word identifiers (IDs). Added to each parsed message is the word count and time when the word arrived. The parser provides stale and skipped indication for each word.

- Snarfing of traffic and tags into a FIFO 16K words deep. A content identifier is added to each word entering the FIFO to identify the type of word (Data Hi/Lo, High/Low/Micro Time, Error, FIFO full/empty) and the bus it appeared on 0-7. The filtering (data selection) into the FIFO is based on both the ID and how full the FIFO is. This allows the user to ensure that the FIFO never fills and any data removed is determined before hand.

- · Parsing and snarfing even with 100% utilization of all busses.