The Low-Powered, High-Integrity Future of Defense and Aerospace Embedded Computing

In the last 10 years, the electronics market has seen an increased demand for smaller, more power-efficient processors. Offering all the performance and reliability without the steep price tag or high power consumption of other market competitors, Arm architecture has quickly become the technology of choice in this venue. More recently, the military and aerospace embedded computing industry has taken notice of Arm's undeniable advantages for deployed operations - low power, low cost, secure, high integrity computing, all in the coveted size, weight, and power (SWaP)-optimized footprint required by Defense and Aerospace platforms. Arm's RISC- (Reduced Instruction Set Computing) based architecture provides a streamlined instruction set that has far surpassed the Intel backward compatibility-focused x86 chip technology in microprocessor sales and offers a more flexible, simplified option for modern embedded computing.

Arm has created a variety of microprocessor designs, each with varying performance and power levels. Arm then licenses its technology to over 1000 industry-leading companies who use the technology to create silicon and other development tools. Together with a large software ecosystem and multiple vendor support, Arm's cutting-edge processors are built to suit the needs of almost all industries and markets. This white paper will focus on three Arm-based cores - the A7, A53, and A57 - and their benefits to embedded computing.

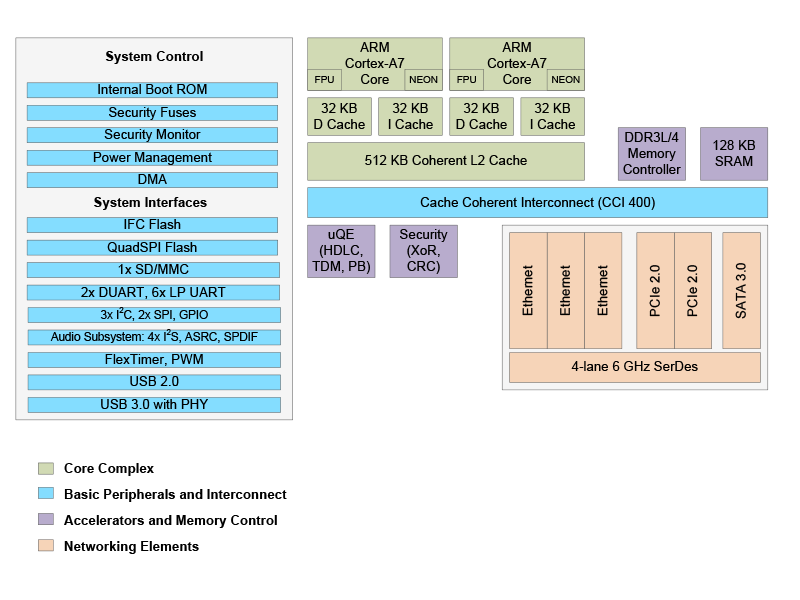

Cortex-A7

The Cortex-A7 is the most power-efficient processor Arm has developed to date. It is purpose-built to provide high-performance computing to low-powered, SWaP-constrained embedded applications, and delivers more single-thread performance than its Cortex-A5 counterpart. In fact, a dual-core A7 processor can even provide higher performance than a Cortex-A9 at lower power.

Implementing the Armv7 architecture, the A7 utilizes an energy-efficient 8- to 10-stage pipeline. The A7 is built on Arm's MPCore multicore technology, which enables cores to shut down when not in use or work together to efficiently share a workload when higher performance is required, maximizing performance while controlling power usage. The A7 provides an integrated low-power L2 cache, which is designed to lower transaction latencies and provide better OS support for the cache's maintenance.