When purchasing a car, there is often a desire to buy a high-performance sports car. The thrill of having a car that can outrun everyone else can be enough sometimes to justify the high cost of many of these automobiles. But how often can you enjoy the maximum performance of these vehicles? Whether it’s road congestion, the restrictive speed limits, or just pure safety concerns, it is rare you fully experience the true capability of the sports car.

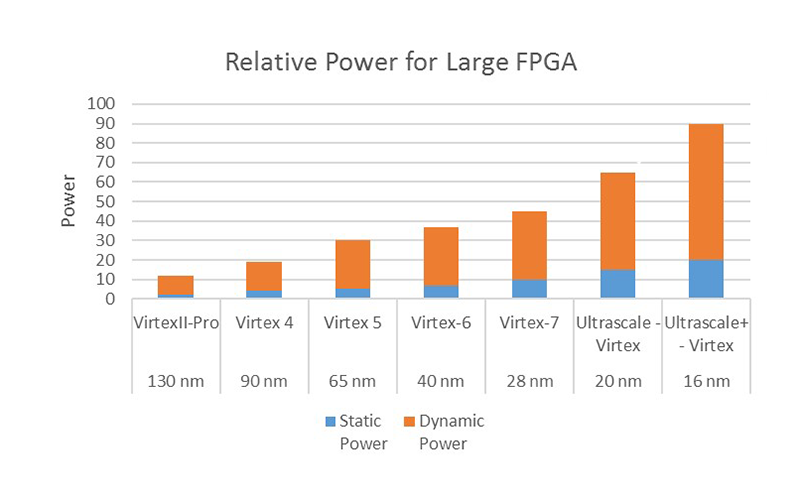

While not as exhilarating as a sports car, being able to fully exercise the capability of the latest generation of FPGAs is also getting harder to do. The fundamental problem is the power of the latest generation FPGAs is out-pacing the ability to cool them, especially in more rugged environments. Below is a graph of the approximate power consumption of the last several generations of FPGAs at high temperatures, focusing on one of the larger parts available for that family.

Figure 1: FPGA Power Consumption Trend for Large FPGAs

A couple of trends can be seen here: one is the obvious increase in total power. The other is the increase in static power, which is caused by leakage current in the transistors. The latter power is the worst because leakage current occurs even if the FPGA is not doing any processing at all, and it eats into the useful power budget for the FPGA. Static power, unlike dynamic power, also increases exponentially with temperature. Therefore, while static power is generally not a huge concern when operating FPGAs in a benign environment, it is a major concern when operating FPGAs at their maximum temperatures.

If the FPGA is large and burning a lot of power, even at room temperature, the die temperature can heat up significantly despite a benign ambient temperature. This is not a problem that is unique to FPGAs. It is a function of the geometry of the silicon used to make the FPGA and therefore common to processors and GPGPUs as well.

Another trend is that FPGA I/O is also consuming more power. As many interface speeds are increasing and SERDES interfaces are becoming more dominant, I/O power can contribute 20-30 watts or more to power consumption. Add that to leakage current and you begin to wonder, what power is left over for processing inside the FPGA?

This gets to the crux of the problem. In order to be able to truly take advantage of the vast processing capability of FPGAs in rugged environments, more needs to be done to enable higher-powered FPGAs to exist in these rugged environments. Otherwise, either FPGAs will be underutilized and their advertised capabilities cannot be fully achieved, or smaller FPGAs need to be used instead.

Download the white paper to learn more.

- FPGAs

- Ruggedization

- Cooling methods

- Convection-cooling

- Conduction-cooling

- Air-flow-Through (AFT)

- VITA 48

- Thermal resistance